微電子研究所微波器件與集成電路研究室化合物半導體基超高速數模混合電路課題組經過全力攻關,日前在超高速數模混合芯片的研制領域取得整體突破。課題組成功研制多款基于1um GaAs HBT工藝的超高速數模混合電路芯片,該系列芯片全部采用自主創新的架構,其性能已達到或超越國際同類芯片的最高水平。

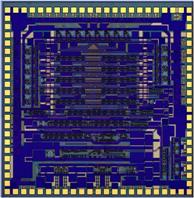

4GHz 32bit超高速DDS芯片

基于1um GaAs HBT工藝的4GHz 32-bit超高速直接數字頻率合成器(Direct Digital Synthesizer, DDS)芯片,測試結果表明其可在4GHz時鐘頻率下正常工作,可生成0~2GHz范圍內的頻率捷變正弦波,其最差無雜散動態范圍(SFDR)大于40dBc,芯片面積為

![]() ,其工作時鐘頻率超過國外同類型產品。

,其工作時鐘頻率超過國外同類型產品。

圖1 4GHz 32bit DDS芯片照片

圖2 4GHz 32bit DDS芯片測試波形和輸出頻譜圖

研究中采用自主創新的DDS架構,保證了芯片在時鐘頻率為GHz的條件下正常工作,該款芯片含有近萬只HBT晶體管,電阻2600余只,是目前國內實現的首款含有萬只晶體管的DDS。該款芯片的內部還設計了Strobe電路用于調整輸入的控制字與內部時鐘的同步,使得輸出正弦波形可在頻率切換時保持相位連續。該芯片是目前國內所報道的時鐘速度最快的32bit的 DDS,其架構與設計均達到國際一流水平,它的研制成功為國內超高速DDS的發展起到重要的推動作用。

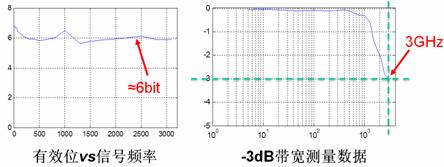

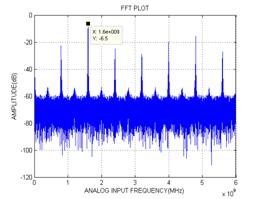

2GSps 8bit 超高速ADC芯片

基于1um GaAs HBT工藝的8-bit超高速模數轉換器(Analog to Digital Converter, ADC)芯片,其測試結果表明可在300MHz~2GHz采樣頻率下正常工作,模擬信號-3dB全功率帶寬達到3GHz,在3GHz輸入帶寬內有效位數(ENOB)達到6bit,SFDR大于45dBc,測試結果見圖3所示,這是國內首次報道的2GSps 8bit的超高速ADC芯片。

圖3 2GSps 8bit ADC芯片測試結果

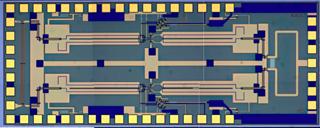

該款ADC芯片采用折疊內插架構,充分發揮異質結晶體管(HBT)的潛力,在達到高精度的同時保持較小的電路規模。芯片集成了約5000只GaAs HBT晶體管,面積為

![]() ,ADC的評估板以及芯片照片如圖4所示。芯片的輸出數據采用標準LVDS電平,可以和商用FPGA芯片直接相連;芯片內部帶有溫度監控電路,芯片的每個管腳都做了ESD保護處理,這些設計使得ADC芯片具有一定的實用性。該款芯片是一款通用芯片,可以應用于寬帶雷達、超寬帶通信、高速示波器等領域,具有廣闊的應用前景。

,ADC的評估板以及芯片照片如圖4所示。芯片的輸出數據采用標準LVDS電平,可以和商用FPGA芯片直接相連;芯片內部帶有溫度監控電路,芯片的每個管腳都做了ESD保護處理,這些設計使得ADC芯片具有一定的實用性。該款芯片是一款通用芯片,可以應用于寬帶雷達、超寬帶通信、高速示波器等領域,具有廣闊的應用前景。

圖4 2GSps 8bit ADC評估板和芯片照片

12.5GSps超高速單比特比較器芯片

基于1um GaAs HBT工藝的單比特超高速比較器芯片,測試結果表明,超高速單比特ADC芯片在 DC-12.5GHz 時鐘頻率下工作正常,輸入信號靈敏度為-20dbm,對DC-18GHz輸入模擬信號采樣數據正確。考慮到多芯片同步的應用需求,芯片內部集成了時鐘同步電路,可以有效實現多芯片的同步工作。為了滿足高速率的要求,芯片輸出采用LVDS接口。該芯片集成約1600個GaAs HBT晶體管,芯片面積為2.3mmx2.3mm。電路采用-5.2V/+3.3V雙電源供電,總功耗為3.2W。單比特ADC芯片照片及測試數據頻譜分析如圖5所示。該芯片的各項性能指標均達到了國外同類型芯片產品的水平,目前正與用戶單位合作開展應用驗證工作。

圖5單比特ADC芯片照片及測試數據頻譜分析圖

Ka波段矢量調制器和解調器芯片

研制成功基于1um GaAs HBT工藝的Ka波段(26.5~40GHz)矢量(IQ)調制/解調器。其中,調制器芯片面積為1.35mm×3.5mm,如圖6所示,采用5V電源電壓,總功耗為200mW.在載波為25~35GHz,基帶調制速率達到2Gb/s,QPSK調制星座圖錯誤向量幅度(Error Vector Magnitude, EVM)小于6%。解調器芯片面積1.35mm×3.5mm,采用4.5V電源電壓,總功耗為350mW。解調器可工作的載波頻率為25~35GHz,解調基帶速率可達到2Gb/s. 輸出I路與Q路相位誤差<5°,幅度誤差<0.5dB。

圖6 Ka 波段I/Q失量調制器芯片照片

該系列芯片的研制成功標志著微電子所在超高速數模混合電路研制和產品化道路上邁出了重要一步,充分展示了微電子所在超高速數模混合電路設計方向的強大實力。研究組成員將會繼續努力,為國內超高速數模混合電路的實用化發展作出貢獻。

粵公網安備 44030902003195號

粵公網安備 44030902003195號