NI矢量信號收發(fā)器的FPGA編程

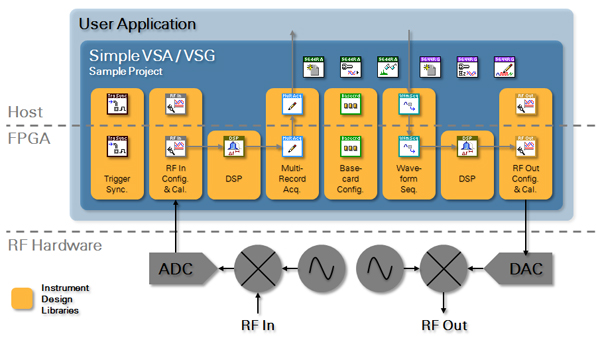

圖5. Simple VSA/VSG項(xiàng)目樣例在主機(jī)和FPGA上聚集儀器設(shè)計(jì)庫,提供了一個(gè)VSA和VSG用戶所熟悉的起點(diǎn)

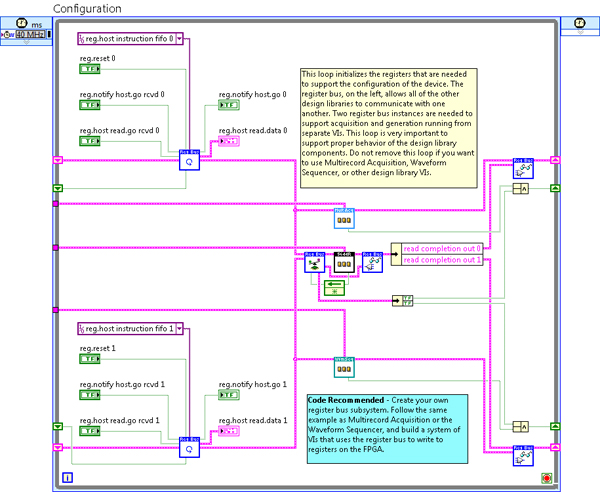

從Simple VSA/VSG項(xiàng)目樣例的FPGA VI開始,有四個(gè)主要回路,一些附加功能位于過程subVI內(nèi)。為配置NI VST的所有可編程組件,以及FPGA上的一些儀器設(shè)計(jì)庫,配置回路從主機(jī)處接收寄存器和設(shè)置,然后將其分布至各個(gè)FPGA子系統(tǒng)和外部電路。為了提高性能以及使主機(jī)上的多個(gè)過程均能夠獨(dú)立訪問,有兩個(gè)寄存器總線。一個(gè)用于采集,另一個(gè)用于生成,并且每一個(gè)都必須能夠配置共享資源,例如計(jì)時(shí)。

圖6. 配置回路負(fù)責(zé)接收主機(jī)的數(shù)據(jù)以及對儀器進(jìn)行編程

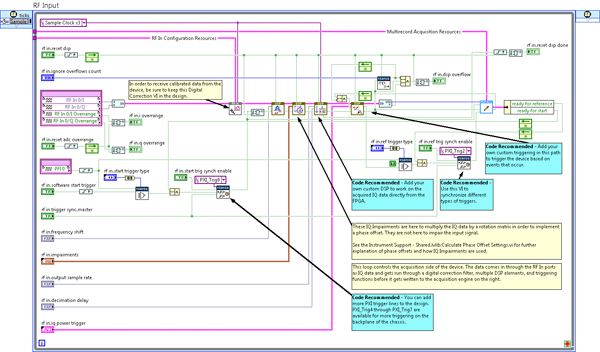

RF輸入回路獲取模數(shù)轉(zhuǎn)換器(ADC)的數(shù)據(jù);進(jìn)行復(fù)矢量校準(zhǔn);并進(jìn)行頻移、相位校準(zhǔn)、減損,以及可變、部分、防混疊抽選。另外,RF輸入回路還實(shí)現(xiàn)了同步以及數(shù)字式功率水平觸發(fā),然后將數(shù)據(jù)寫入FIFO,并最終寫入DRAM。

圖7. RF輸入回路以可配置I/Q速率生成已校準(zhǔn)數(shù)據(jù),并將其寫入DRAM。

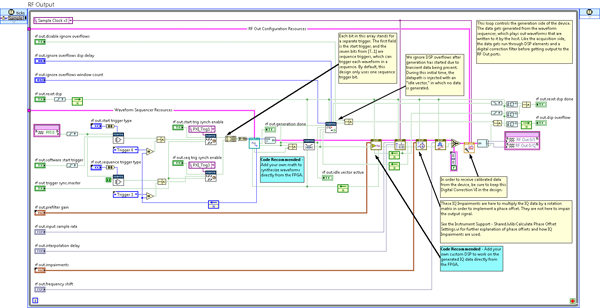

RF輸出循環(huán)類似于RF輸入循環(huán),但是操作順序相反。來自DRAM的數(shù)據(jù)進(jìn)行內(nèi)插、定標(biāo)、頻移、相位校準(zhǔn)、內(nèi)插、校準(zhǔn),然后通過數(shù)模轉(zhuǎn)換器(DAC)生成。另外還有觸發(fā)和同步所用信號。

圖8. RF輸出循環(huán)檢索來自DRAM的數(shù)據(jù)然后生成數(shù)據(jù)

過程子VI包含有循環(huán)和狀態(tài)機(jī),實(shí)現(xiàn)了多數(shù)據(jù)記錄采集和DRAM控制器對波形的排序。這些子VI包含了大量代碼,滿足了大帶寬和低滯后性能要求,確保這些子VI能夠在全速率ADC數(shù)據(jù)轉(zhuǎn)換下溢出,以及產(chǎn)生全速率DAC數(shù)據(jù)而不發(fā)生下溢,同時(shí)仍然與主機(jī)之間進(jìn)行波形數(shù)據(jù)傳輸。

讀取循環(huán)實(shí)現(xiàn)的功能可以存在于多記錄采集過程之內(nèi),然而為了方便起見而將其顯示出來。該循環(huán)可以再數(shù)據(jù)離開DRAM時(shí)并在被發(fā)送到主機(jī)前進(jìn)行數(shù)據(jù)處理。此路徑在它自己的回路之內(nèi),從而那些并不符合120 MHz RF輸入和輸出回路的定時(shí)要求的IP仍然可以使用。為了適應(yīng)這種IP,稍微降低此回路速率并不會影響讀取性能,然而如果降得過多,則只會增加數(shù)據(jù)到達(dá)主機(jī)所需時(shí)間。這樣即使采樣內(nèi)存被填滿了,也不會丟失樣點(diǎn)或破壞數(shù)據(jù)。

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號