采用PLL技術(shù)的接收機(jī)射頻前端的設(shè)計(jì)

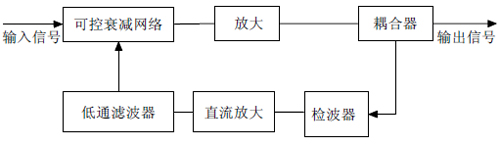

圖2、AGC 電路原理圖

3.2、接收機(jī)本振鎖相環(huán)路的設(shè)計(jì)

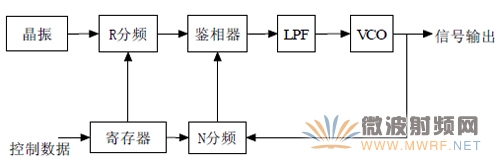

圖3、瑣相環(huán)原理圖

接收機(jī)通過混頻實(shí)現(xiàn)射頻變頻到基帶,而且采用的是超外差式結(jié)構(gòu)的接收機(jī),因此在本設(shè)計(jì)中我們需要設(shè)計(jì)兩個(gè)本振源。系統(tǒng)設(shè)計(jì)要求本振信號(hào)頻率精度和穩(wěn)定度高,相位噪聲小,所以選擇鎖相環(huán)實(shí)現(xiàn)本振生成。鎖相環(huán)是一種建立在相位負(fù)反饋基礎(chǔ)之上的閉環(huán)控制系統(tǒng)[5],對(duì)相位噪聲和雜散具有很好的抑制作用,在電視,儀器,通信等領(lǐng)域得到了廣泛的應(yīng)用。該接收機(jī)本振設(shè)計(jì)我們采用ADI 公司的瑣相環(huán)系列芯片[6-7]做本振的設(shè)計(jì),其可應(yīng)用于無(wú)線射頻通信系統(tǒng),是性價(jià)比很高的電荷泵鎖存芯片。

在設(shè)計(jì)中,通過編寫程序由單片機(jī)實(shí)現(xiàn)提供給瑣相環(huán)的CLOCK,DATA 和LE 信號(hào),在頻率合成器芯片內(nèi)部完成參考晶振R 分頻和壓控振蕩器N 分頻相位的比較,并且轉(zhuǎn)換成相應(yīng)的線性電壓后,經(jīng)過3 階環(huán)路濾波器濾出高頻干擾信號(hào)后,得到一個(gè)穩(wěn)定電壓來(lái)控制壓控振蕩器的輸出,最終的信號(hào)頻率通過兩個(gè)鎖相芯片被分別鎖定在第一和第二本振頻率上。

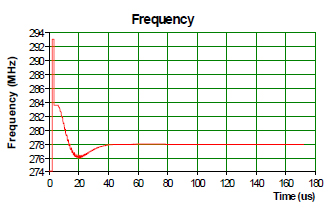

圖4、第二本振的瑣相環(huán)入瑣過程

從圖4,第二本振的入鎖過程我們可以看到瑣相環(huán)的入鎖時(shí)間在40us 左右,滿足要求。采用單片機(jī)提供鎖相的控制字的優(yōu)點(diǎn)就在于:利于及時(shí)修改,便于操作。下面是本振的實(shí)際電路圖,包括第一本振鎖相芯片和第二本振鎖相芯片,其共用一個(gè)10MHz 的晶振:

圖5 實(shí)際的第一、第二本振電路圖

3.3、解調(diào)

接收機(jī)解調(diào)部分采用AD 公司的解調(diào)芯片,該芯片工作頻率從50MHz 到1000MHz,包括正交下變頻器,內(nèi)置可控增益放大器和偏置電路。其內(nèi)置VGA,控制電壓由外部提供并可調(diào)增益大小,增益可調(diào)范圍為44dB。

輸入芯片的中頻信號(hào)為了滿足芯片的輸入功率要求,加入了功率驅(qū)動(dòng)放大鏈路,經(jīng)放大后輸入解調(diào)芯片的功率約為-40dBm 左右。因?yàn)榻庹{(diào)芯片對(duì)第二本振信號(hào)內(nèi)置了二分頻器,所以第二本振信號(hào)頻率應(yīng)該是所需頻率的兩倍。

輸出的I/Q 兩路信號(hào)分別再經(jīng)過運(yùn)放電路進(jìn)行放大,最終輸出給數(shù)字基帶部分進(jìn)行處理[8-9]。

4、實(shí)際測(cè)試結(jié)果

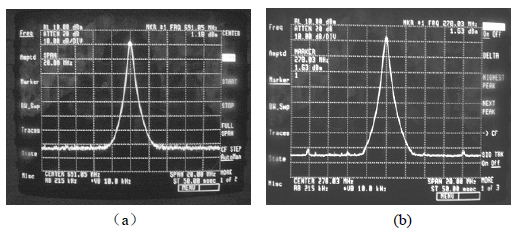

實(shí)際測(cè)時(shí),輸入信號(hào)頻率為831MHz,通過在單片機(jī)編寫控制字程序設(shè)置第一本振和第二本振的輸出頻率,第一次混頻后得到的中頻信號(hào)頻率為140MHz,第二次混頻后解調(diào)輸出頻率為1MHz 的I/Q 兩路信號(hào)。本振的輸出信號(hào)如下圖所示:

圖6、(a)第一本振輸出(b)第二本振輸出

粵公網(wǎng)安備 44030902003195號(hào)

粵公網(wǎng)安備 44030902003195號(hào)