隨著半導(dǎo)體制造能力允許在單塊芯片上集成數(shù)千門邏輯電路,系統(tǒng)級芯片(SoC)開始占據(jù)未來IC技術(shù)的中心。不過,當(dāng)今天人們在談?wù)揝oC時(shí),他們實(shí)際談?wù)摰闹皇遣糠窒到y(tǒng)——僅是把數(shù)字基帶與數(shù)據(jù)轉(zhuǎn)換器、一些高速模擬IO、甚至一些射頻電路集成在一起,只要它不會太復(fù)雜。

由于工藝技術(shù)的不兼容性,RF集成通常被認(rèn)為是一種基本上尚未解決的SoC挑戰(zhàn)。在數(shù)字裸片上集成RF電路會限制良品率或?qū)е赂甙旱臏y試成本,從而極大地增加生產(chǎn)成本。

但問題比這更復(fù)雜和微妙。從SoC系統(tǒng)層面上來看,RF集成將給硬件器件的電路設(shè)計(jì)、物理實(shí)現(xiàn)及制造與測試帶來一些困難的開發(fā)挑戰(zhàn)。

現(xiàn)在,RF芯片設(shè)計(jì)者有了另一種選擇。CMOS制造工藝技術(shù)的最新發(fā)展克服了RF集成障礙,使開發(fā)者可以將RF處理移到數(shù)字域中。芯片設(shè)計(jì)者不必費(fèi)勁去設(shè)計(jì)和實(shí)現(xiàn)模擬器件,相反,他們可以采用數(shù)字RF技術(shù),并利用熟悉的工具和工藝來處理RF信號。

不可能只集成一種無線電

為了適應(yīng)手機(jī)或PDA的小外形尺寸,這要求在一塊芯片上同時(shí)集成數(shù)字、模擬及RF,否則成本與外形尺寸限制將阻礙手機(jī)配置新的功能。集成的無線電只有傳統(tǒng)無線電一半的硅面積,占有一半的板空間,消耗大約一半的功率。因此,無線電集成在滿足手機(jī)設(shè)計(jì)目標(biāo)方面提供了極大的優(yōu)勢。

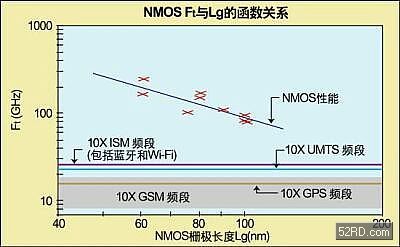

圖1:跟蹤每個工藝節(jié)點(diǎn)的截止頻率可以評估哪

些通信頻段能夠在數(shù)字域中進(jìn)行處理。

讓我們來看看3G手機(jī)的數(shù)據(jù)處理要求。在數(shù)字域,用戶希望擁有更高分辨率的彩屏顯示器、需要額外存儲器與圖形資源的游戲、PDA應(yīng)用功能以及諸如照相、視頻會議及音頻播放等多媒體功能。在RF方面,一部手機(jī)集成好幾種無線電并非是不合理的,它們包括:

* 很多GSM手機(jī)都支持全部四個頻段——?dú)W洲的蜂窩與DCS以及美國的不同蜂窩頻率與PCS

* 2.1 GHz的UMTS

* 用于定位與同步的GPS

* 用于PAN連接的藍(lán)牙

* 用于網(wǎng)絡(luò)連接的WiFi,如果是2.4 GHz 802.11b/g,則可共用藍(lán)牙無線電

* 數(shù)字電視(DTV)

* 數(shù)字音頻廣播與調(diào)頻廣播等

今天,板上的RF器件數(shù)已超過總器件數(shù)的一半,而且一種簡單的無線電就要占去手機(jī)印制電路板(PCB)40%的面積。如果靠增加無線電來支持藍(lán)牙、GPS及WLAN等功能,那么會顯著增大這些數(shù)字。盡管無線電能共用一些電路,但如果它們想要裝入一部設(shè)備中,則必須比它們今天的尺寸小。

存在的問題

集成數(shù)字、模擬及RF電路所遭遇的實(shí)際問題向那些對整體硅集成充滿熱情的人潑了一盆冷水。對于在SoC上集成復(fù)雜RF電路的設(shè)計(jì)來說,可用的EDA開發(fā)工具仍存在許多有待改進(jìn)之處。

用于同時(shí)驗(yàn)證數(shù)字與RF電路的工具仍處于發(fā)展的初期階段,更談不上同時(shí)對設(shè)計(jì)進(jìn)行驗(yàn)證與測試。其他局限還包括小器件的不良匹配、高1/f噪聲、以及缺少帶足夠模擬特征的片上無源器件(電阻、電容及變?nèi)荻O管)等。

盡管存在這些挑戰(zhàn),集成仍然是使智能電話降低無線電設(shè)計(jì)的成本、功耗及復(fù)雜性的基本手段。為了使無線電集成成為現(xiàn)實(shí),業(yè)界要求在晶圓工藝、系統(tǒng)設(shè)計(jì)及電路設(shè)計(jì)層面上有顯著的技術(shù)進(jìn)步。盡管采用SoC的設(shè)計(jì)者并不關(guān)心許多SoC技術(shù)挑戰(zhàn),但了解這些挑戰(zhàn)也很重要,因?yàn)樗鼈儧Q定了實(shí)際器件的能力與局限。例如,盡管使用雙極或BiCMOS工藝集成RF在技術(shù)上是可行的,但測試器件時(shí)的良率限制及高昂成本使得這些器件未必能實(shí)現(xiàn)大批量或商業(yè)生產(chǎn)。

集成硅鍺(SiGe) BiCMOS技術(shù)也是可能的做法。但硅鍺技術(shù)一般比先進(jìn)的數(shù)字CMOS工藝落后1個或2個工藝節(jié)點(diǎn)。由于手機(jī)需要越來越多的處理資源,硅鍺工藝無法使數(shù)字部分(特別是存儲器)的裸片成本保持最低。

即使CMOS RF集成也有它的挑戰(zhàn)。模擬混頻器、濾波器及放大器等的實(shí)現(xiàn)都很困難,尤其隨著電壓下降,新工藝節(jié)點(diǎn)早期的器件建模一般都不足以達(dá)到模擬模塊設(shè)計(jì)所需的高精度參數(shù)建模。業(yè)界要求有重大的設(shè)計(jì)創(chuàng)新,從而允許無線電被集成在標(biāo)準(zhǔn)的CMOS中,并充分利用CMOS技術(shù)的優(yōu)勢。

數(shù)字RF集成解決RF集成問題的一種不同方法是完全避免它們,這可通過將RF器件的功能轉(zhuǎn)換到數(shù)字域來實(shí)現(xiàn)。

通過在CMOS數(shù)字域處理RF信號,就沒有必要使用復(fù)雜且昂貴的模擬掩模。芯片設(shè)計(jì)也變得更加容易,因?yàn)殚_發(fā)者在仿真時(shí)可以更容易了解系統(tǒng)細(xì)節(jié),并能通過整合可編程軟硬件元素來執(zhí)行處理,從而增強(qiáng)對信號處理過程的控制。

例如,從電源耦合到發(fā)射與接收壓控振蕩器(VCO)上的噪聲會影響整體系統(tǒng)效率。因此,大多數(shù)無線電路板設(shè)計(jì)都要求使用調(diào)節(jié)器及相關(guān)無源器件來解決此問題。將這些器件集成在無線電收發(fā)器中,意味著簡單的去耦電容是所需的、要求與電池直接相連的唯一外部元件,從而可簡化設(shè)計(jì)并節(jié)省板空間。

設(shè)計(jì)者還可選擇將數(shù)字調(diào)諧及自校準(zhǔn)功能集成到VCO中,并通過集成環(huán)路濾波器來擴(kuò)大VCO的調(diào)諧范圍。

為使數(shù)字電路能處理模擬信號,它們必須工作在極高的速度。器件截止頻率(Ft)是一種用來評價(jià)工藝處理RF信號能力的簡單方法(參見圖1)。

總的原則是,F(xiàn)t應(yīng)大約為工作頻率的10倍。例如,要處理1.9 GHz的信號,F(xiàn)t就必須大約為19 GHz。缺少足夠的Ft是老式CMOS工藝的一個主要局限,但今天的90納米技術(shù)可提供超過100 GHz的Ft性能。這種極高的Ft很容易就超過蜂窩手機(jī)無線電的所有要求。

數(shù)字RF處理在過去十年間已經(jīng)登上歷史舞臺,但隨著SoC轉(zhuǎn)向90納米工藝,“高頻”的含義將隨著Ft的提高而被重新定義。今天,運(yùn)行在1 GHz的DSP能處理整個數(shù)字域中的“高頻”信號,甚至可用軟件來動態(tài)控制信號處理。

最近,TI公布了第二代藍(lán)牙SoC 芯片——BRF 6150,這款芯片給出了用CMOS工藝進(jìn)行SoC集成如何能簡化設(shè)計(jì)并降低板空間要求和系統(tǒng)成本的一個范例。BRF6150在一個4.5mm x 4.5mm的封裝內(nèi)集成了藍(lán)牙基帶、數(shù)字RF及天線開關(guān),使設(shè)計(jì)者能在50平方毫米的面積內(nèi)增加藍(lán)牙功能(見圖2)。

集成式BRF6150的功耗比同類解決方案低30%,且其待機(jī)電流僅為6uA。它直接與電池連接,無需使用外部調(diào)節(jié)器。該芯片僅需11個外部器件,從而簡化了設(shè)計(jì)復(fù)雜性。這種集成式藍(lán)牙芯片是提高集成度和轉(zhuǎn)向真正數(shù)字無線電的典型成果。

藍(lán)牙之外

今天,我們能集成藍(lán)牙的一個主要原因是,它采用功率相對較低、僅需短距離傳輸?shù)男盘枴,F(xiàn)代手機(jī)要求有-106dBm量級的靈敏度,且必須能對鄰近頻段有60dB的抑制,并采用可避免將相位噪聲引入接收頻段的振蕩器。這些極端的性能要求使無線電集成具有更大的挑戰(zhàn)。使設(shè)計(jì)者可以滿足這些苛刻設(shè)計(jì)約束的許多關(guān)鍵器件,已經(jīng)能夠在數(shù)字域中找到解決方案。例如,全集成的數(shù)字頻率合成器已經(jīng)面市,它的所有內(nèi)部元件都在片上而且沒有外部引腳,這是RF集成技術(shù)的一個重要里程碑。

集成的另一個關(guān)鍵優(yōu)勢是,通過使用更小尺寸的工藝技術(shù)進(jìn)行設(shè)計(jì),無線電能工作在更低的電壓上。在大多數(shù)情況下,在較低的電壓上工作絕對是一個優(yōu)勢,因?yàn)槟塬@得更長的電池使用壽命(這是在現(xiàn)有手機(jī)上引入新功能的一個主要障礙)以及具有更小的散熱。

但低電壓同時(shí)也會帶來一些基本問題,如動態(tài)范圍。動態(tài)范圍挑戰(zhàn)會因?yàn)闊o線通信的遠(yuǎn)近而顯現(xiàn)出來。例如,如果手機(jī)A靠近蜂窩而手機(jī)B遠(yuǎn)離蜂窩,則手機(jī)B就必須在最大功率上發(fā)射信號,才能連接蜂窩。

當(dāng)信道A和信道B處于不同頻率上時(shí),信道B的高功率信號有可能泄漏至信道A中,故要求手機(jī)A具有抑制遠(yuǎn)信道干擾的能力,以便能在有高功率發(fā)射存在的情況下接收微伏信號。幸運(yùn)的是,像動態(tài)范圍這些問題可通過前端處理這種直接的方式來加以解決。

產(chǎn)生適合用來驅(qū)動天線的高功率信號是SoC集成面臨的另一個關(guān)鍵挑戰(zhàn)。通常,廣域網(wǎng)(WLAN)所用功放的高功率、高電壓及高散熱等因素,使它們不適合用深亞微米CMOS工藝來進(jìn)行集成。

但需指出的是,這些問題主要與現(xiàn)有廣域網(wǎng)(如GSM 及CDMA)有關(guān),而距離較短的個人區(qū)域網(wǎng)(PAN)以及局域網(wǎng)(LAN)可以采用功放集成。

在這種SoC設(shè)計(jì)中,將功放靠近數(shù)據(jù)處理器放置可執(zhí)行自動系統(tǒng)校準(zhǔn),從而提高整體系統(tǒng)性能。此外,由于通過RF集成可以節(jié)省成本、板空間及功耗,數(shù)字RF還能加快一些新興短距離網(wǎng)絡(luò)(包括UWB、Zigbee及網(wǎng)格網(wǎng)絡(luò)等)的開發(fā)。

批量驗(yàn)證

模擬RF集成的另一個主要障礙是驗(yàn)證,這甚至比保持手機(jī)所要求的大批量生產(chǎn)的良品率更令人生畏。生產(chǎn)用RF測試儀通常不能測試數(shù)字邏輯陣列,而邏輯測試儀又不能提供模擬或RF測試能力。但我們既不能讓大型SoC的RF部分對良品率產(chǎn)生很大的影響,也不能讓它延緩SoC向最新工藝節(jié)點(diǎn)的移植。

通過將RF功能移到數(shù)字域,數(shù)字RF處理使得測試和驗(yàn)證無線電的過程接近于只有邏輯電路的情況。盡管永遠(yuǎn)都不可能實(shí)現(xiàn)完全的移植(總是存在一定的模擬與混合信號功能),但數(shù)字處理技術(shù)可用來提高測試與驗(yàn)證過程的效率及可靠性。

采用數(shù)字RF,我們可以完全分析在SoC上的基帶信號特征,而且一些外部模擬器件也可以實(shí)現(xiàn)閉環(huán)測試,以評估信號質(zhì)量。采用這種方式,我們能夠在系統(tǒng)級,而不只是在功能模塊級上對無線電性能進(jìn)行測量。

這不僅能減少所需測量的數(shù)量,而且能簡化驗(yàn)證過程。SoC可帶有自檢測能力,以執(zhí)行自校準(zhǔn)并減少參數(shù)變化對良品率的影響。這能將良品率維持在缺陷密度限制以內(nèi),并將無線電測試成本降低至一個很低的水平。此外,數(shù)字RF模塊還能保持進(jìn)行工藝移植的能力,從而可對芯片進(jìn)行縮放,這也是大批量器件生產(chǎn)的一個重要要求。

在數(shù)字域?qū)崿F(xiàn)RF功能還能通過執(zhí)行系統(tǒng)級優(yōu)化來減少器件成本及復(fù)雜性。例如,處理來自多個無線電的很多頻率,不只是要求將多個無線電放在同一塊裸片上。通過系統(tǒng)級設(shè)計(jì),設(shè)計(jì)者可采用適當(dāng)?shù)碾娐穪頊p少帶內(nèi)寄生信號的產(chǎn)生。設(shè)計(jì)者還能開發(fā)新的架構(gòu),以實(shí)現(xiàn)硬件共用(例如兩個無線電共用一個功能塊等),從而進(jìn)一步減小無線電尺寸。由于這些新架構(gòu)主要是以數(shù)字邏輯實(shí)現(xiàn),所以設(shè)計(jì)者可采用熟悉的EDA仿真與綜合工具,以及數(shù)字測試與制造測試套件。

RF無疑是SoC集成的下一個主要挑戰(zhàn),但隨著CMOS工藝等制造技術(shù)的進(jìn)一步發(fā)展,RF處理已開始轉(zhuǎn)變成數(shù)字域中的設(shè)計(jì)問題。

隨著每個工藝節(jié)點(diǎn)的尺寸減小及晶體管速度的提高,數(shù)字RF處理將能適用于越來越多的通信頻段。RF集成不再是一個是否可行的問題,而且SoC芯片最終能變成在單個芯片上真正完整的系統(tǒng)。

作者:Bill Krenik

無線高級架構(gòu)經(jīng)理

TI公司

Gene Frantz

美國數(shù)字信號處理專家

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號