網(wǎng)站首頁(yè) > 資料查詢 > 教程/講義 > 測(cè)試測(cè)量

Tektronix高速信號(hào)互連測(cè)試和驗(yàn)證解決方案

| 資料語(yǔ)言: | 簡(jiǎn)體中文 |

| 資料類別: | PDF文檔 |

| 瀏覽次數(shù): | 0 |

| 評(píng)論等級(jí): | |

| 更新時(shí)間: | 2014-07-27 23:18:25 |

| 資料查詢: | 您可以通過(guò)企業(yè)官網(wǎng)、京東、出版社等官方渠道下載或購(gòu)買。 |

日程安排

在高速串行數(shù)據(jù)技術(shù)的推動(dòng)下,性能指標(biāo)日新月異

TDR高速串行互連測(cè)試和驗(yàn)證

– TDR的原理和應(yīng)用

– TDR在信號(hào)完整性SI(Signal Integrity)中的應(yīng)用

泰克公司TDR測(cè)試解決方案

泰克串行數(shù)據(jù)鏈路測(cè)試解決方案

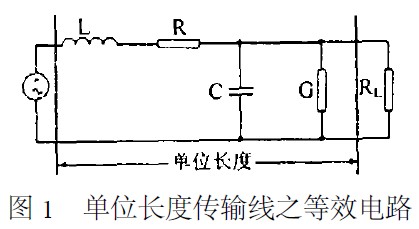

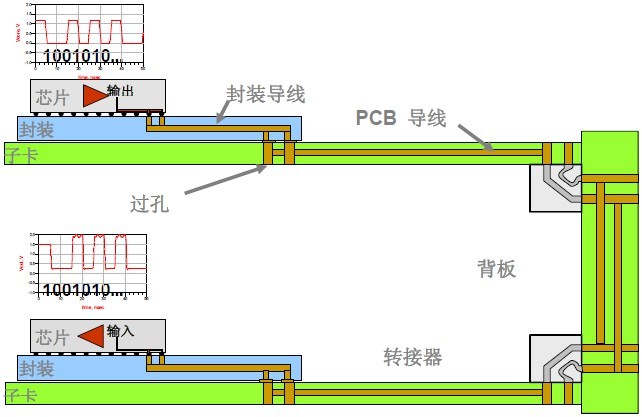

阻抗和信號(hào)完整性問(wèn)題

計(jì)算機(jī)、通信系統(tǒng)、視頻系統(tǒng)和網(wǎng)絡(luò)系統(tǒng)等領(lǐng)域的數(shù)字系統(tǒng)開(kāi)發(fā)人員正面臨著越來(lái)越快的時(shí)鐘頻率和數(shù)據(jù)速率,隨之,信號(hào)完整性變得越來(lái)越重要。在當(dāng)前的高工作速率下,影響信號(hào)上升時(shí)間、脈寬、時(shí)序、抖動(dòng)或噪聲內(nèi)容的任何事物都會(huì)影響整個(gè)系統(tǒng)的性能和可靠性。為保證信號(hào)完整性,必須了解和控制信號(hào)經(jīng)過(guò)的傳輸環(huán)境的阻抗。阻抗不匹配和不連續(xù)會(huì)導(dǎo)致反射,增加系統(tǒng)噪聲和抖動(dòng),在整體上降低信號(hào)的質(zhì)量。

阻抗控制是當(dāng)前許多數(shù)字系統(tǒng)、元器件規(guī)范的一部分,如USB2.0,F(xiàn)irewire(IEEE 1394),PCI Express,Infiniband,Serial ATA,XAUI等規(guī)范。業(yè)內(nèi)已經(jīng)普遍使用仿真工具設(shè)計(jì)高速電路,仿真加快了設(shè)計(jì)周期,最大限度地減少了錯(cuò)誤數(shù)量。但是仿真之后,必須進(jìn)行工程驗(yàn)證來(lái)檢驗(yàn)仿真設(shè)計(jì),這其中就包括阻抗測(cè)量。

溫馨提示:本站不提供資料文件下載,僅提供文件名稱查詢,如有疑問(wèn)請(qǐng)聯(lián)系我們。

粵公網(wǎng)安備 44030902003195號(hào)

粵公網(wǎng)安備 44030902003195號(hào)