1、介紹

在構建嵌入式系統(tǒng)時,不論是為了確保控制循環(huán)能夠可靠的執(zhí)行,還是保證I/O信號能夠被及時響應,或是讓處理速度達到系統(tǒng)應用的要求,定時都是其中的關鍵。構建一套可以滿足定時要求的系統(tǒng),首先從硬件開始進行選擇,必須在尺寸、功耗、處理能力和延遲等方面進行很好的平衡。另外,嵌入式系統(tǒng)的軟件在執(zhí)行調節(jié)、中斷響應和計算任務之間的時間平衡幾個方面扮演著重要的角色。

在考慮定時性能的前提下進行嵌入式軟硬件集成將是一件極其耗時的挑戰(zhàn)。但是,在NI LAbVIEW 2010軟件平臺和RIO硬件平臺的幫助下,構建一套可以滿足絕大部分系統(tǒng)應用需求的可靠的精確定時系統(tǒng)所需要付出的代價將極大降低。繼續(xù)深入下去,了解集成了實時CPU和FPGA的NI RIO硬件系統(tǒng),以及定時特性是如何與LabVIEW 2010無縫集成的,可以幫助工程師、科學家和嵌入式設計人員們利用這套硬件系統(tǒng)構建出健壯的實時響應系統(tǒng)。

2、集成實時CPU和高性能FPGA的NI RIO硬件

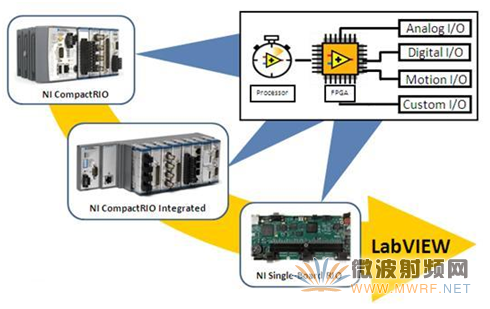

NI嵌入式硬件的目標系統(tǒng)是基于RIO架構的,包括了一個一般用于運行實時操作系統(tǒng)的CPU和一套或多套FPGA。在這樣的集成架構下,用戶可以在FPGA上完成那些需要納秒級定時精度或者大量并行的任務;在CPU上完成諸如浮點計算等密集計算任務。FPGA和CPU之間通過PCI總線進行通信,通過NI-RIO驅動模塊提供的直接明了、功能強大的數(shù)據(jù)傳輸接口, 使用LabVIEW或C可以很容易的進行相關開發(fā)。

最終的結論是:NI-RIO是可以適用于范圍廣泛的嵌入式原型設計,并且具有很高靈活性的平臺。同時,由于NI-RIO框架是很多不同NI硬件目標系統(tǒng)的標準架構,例如NI Single-Board RIO和NI CompactRIO,用戶在部署軟件時,不論是堅固型系統(tǒng)還是經濟型系統(tǒng),都可以最大限度地實現(xiàn)代碼的復用。

圖1. NI-RIO嵌入式設備均基于集成了CPU、FPGA和模塊化I/O的統(tǒng)一架構

例如,Ventura市航空中心使用LabVIEW和NI Single-Board RIO開發(fā)了一套火情監(jiān)控系統(tǒng),用于在聯(lián)邦快遞公司的運輸機上防控火災。在這套系統(tǒng)中,實時CPU負責運行確定性控制算法、網絡通訊和數(shù)據(jù)記錄,F(xiàn)PGA硬件上則執(zhí)行其他的關鍵任務。

3、LabVIEW 2010和內置的定時特性簡化了確定性可靠系統(tǒng)的編程

LabVIEW不單可以使用圖形化的編程界面來編寫目標CPU(包括了運行實時操作系統(tǒng)的CPU)和FPGA(包括RIO目標硬件上的FPGA)程序,同時LabVIEW圖形化編程語言本身也是基于定時和同步概念而設計的。下面的一些例子將說明,LabVIEW結合Real-Time模塊和FPGA模塊是如何讓嵌入式系統(tǒng)的定時變得簡潔明了的。

4、LabVIEW Real-Time模塊集成的定時特性

使用Real-Time模塊和Timed Loop進行確定性的閉環(huán)系統(tǒng)編程

LabVIEW 2010 Real-Time模塊把LabVIEW圖形化編程擴展到了NI實時硬件系統(tǒng)(包括RIO設備)特定的第三方PC上。根據(jù)使用的目標硬件不同,LabVIEW Real-Time模塊會自動在目標硬件上部署與標準的VxWorks或ETS實時操作系統(tǒng)相對應的組件,以保證確定性和精確的實時性。

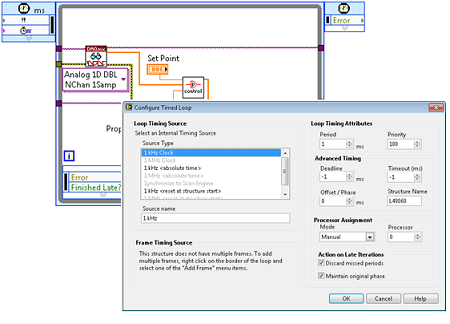

當使用LabVIEW Real-Time模塊進行閉環(huán)控制系統(tǒng)的編程時,通過使用Timed Loop,只需要輕點幾下鼠標,就可以實現(xiàn)周期性執(zhí)行代碼,硬件控制循環(huán)速率同步,定義多種循環(huán)執(zhí)行優(yōu)先級,甚至可以指定某一循環(huán)在某一個CPU內核上執(zhí)行。另外,用戶還可以選擇KHz、MHz或者自定義的外部時鐘來作為循環(huán)定時的基準時鐘。

圖2. LabVIEW Timed Loop可以讓用戶通過簡潔明了的方式實現(xiàn)配置循環(huán)定時、通過硬件I/O進行同步、控制實時代碼執(zhí)行優(yōu)先級、指定代碼執(zhí)行CPU內核等

在多系統(tǒng)間實現(xiàn)Timed Loop的同步

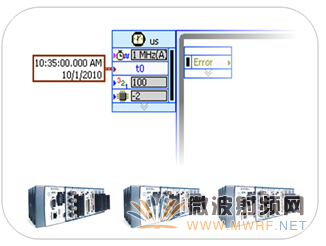

在使用LabVIEW Real-Time模塊編程的嵌入式硬件設備上,用戶可以使用IEEE 1588同步協(xié)議進行多系統(tǒng)間的同步,以保證給定的任務在多系統(tǒng)上是同步執(zhí)行的。根據(jù)用戶使用的硬件設備不同,IEEE 1588同步協(xié)議可以通過軟件、硬件或者軟硬結合這幾種不同方式來實現(xiàn)。

使用LabVIEW Real-Time模塊實現(xiàn)多硬件設備間的軟件同步,將Timed Loop設置為使用絕對時間源即可。在設置好Timed-Loop后,只需要再連接一個起始時間戳,然后選擇運行,就可以在多硬件設備間同時開始循環(huán)的執(zhí)行。

圖3. 用戶可以使用LabVIEW Timed-Loop來實現(xiàn)IEEE 1588同步協(xié)議,在多個分布式的嵌入式設備中實現(xiàn)同步控制(上圖為NI CompactRIO)

使用NI Real-Time執(zhí)行跟蹤工具包進行定時的細節(jié)分析

在LabVIEW Real-Time模塊下使用Real-Time執(zhí)行跟蹤工具包,可以獲取線程和子VI的執(zhí)行時間、優(yōu)先級、繼承關系等多種詳細信息。通過這套工具包,不但可以幫助用戶優(yōu)化實時程序的執(zhí)行情況,更可以幫助用戶發(fā)現(xiàn)諸如優(yōu)先級設置不當、資源競爭等潛在的不穩(wěn)定因素。

在實時硬件上確定性的運行m文件

如果已經有了現(xiàn)成的m文件,用戶可以通過LabVIEW MathScript RT模塊,在使用LabVIEW Real-Time模塊編程的嵌入式系統(tǒng)中使用這些代碼。這種方式從根本上改變了以往從m文件到實時硬件代碼的復雜而繁瑣的遷移過程,使其變得簡潔而迅速。只需要將用戶的m文件通過MathScript節(jié)點嵌入到LabVIEW圖形代碼中,再在LabVIEW項目中將其拖放到實時硬件上,整個遷移過程就完成了。

5、LabVIEW FPGA模塊內置的定時特性

使用單周期定時循環(huán)優(yōu)化FPGA程序

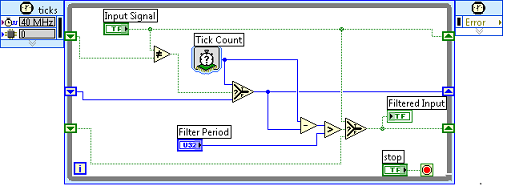

LabVIEW 2010 FPGA模塊中的單周期定時循環(huán)移除了循環(huán)內部的寄存器,用戶可以在其中最優(yōu)化地運行與之相兼容的代碼。這項措施可以使那些需要在硬件上可靠運行的關鍵操作達到最高40MHz的循環(huán)速率。另外,在單周期定時循環(huán)內執(zhí)行的代碼占用的FPGA資源更少,從而可以節(jié)省出更多的資源給其他的任務。

圖4. LabVIEW FPGA模塊中的單周期定時循環(huán)可以讓用戶的這部分代碼達到最高40MHz的循環(huán)速率

使用循環(huán)定時器來調整FPGA代碼的執(zhí)行

想要在FPGA上周期性地執(zhí)行操作其實很簡單,只需要在LabVIEW FPGA的代碼框圖里添加一個循環(huán),然后在其中放置一個循環(huán)定時器就可以了。循環(huán)定時器的定時控制可以根據(jù)需要選擇循環(huán)周期為納秒級、微秒級或者毫秒級的不同硬件時鐘作為定時基準。在默認的40MHz時鐘速率下,循環(huán)定時器可以實現(xiàn)25ns整數(shù)倍的定時周期。

通過中斷對實時程序和FPGA程序的定時進行同步

在FPGA硬件系統(tǒng)中,用戶可以在FPGA程序中產生中斷,通知實時程序各種事件的發(fā)生,例如數(shù)據(jù)采集完畢,發(fā)生錯誤,任務已經完成等等。使用LabVIEW FPGA模塊中的相關中斷函數(shù)結合LabVIEW Real-Time模塊中的Wait on Interrupt方法,用戶可以實現(xiàn)整個嵌入式系統(tǒng)中CPU和FPGA之間的同步。一個系統(tǒng)中最多能夠使用32個中斷。

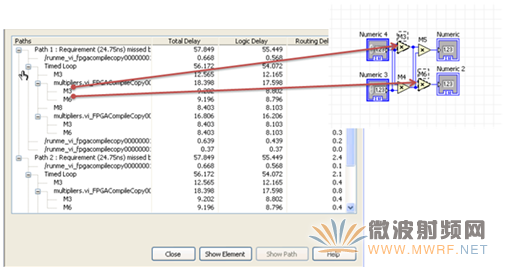

使用關鍵路徑高亮幫助確定系統(tǒng)瓶頸。

在開發(fā)過程中,確定和修正時序錯誤的FPGA代碼是一件耗時費力的事情。為了簡化這一過程,可以使用LabVIEW FPGA模塊的關鍵路徑高亮功能來突出關鍵路徑上的每一步操作,迅速跳轉到出現(xiàn)瓶頸的代碼部分,編寫更高效的代碼或者流水線來對瓶頸進行修正。

圖5. LabVIEW FPGA模塊的關鍵路徑高亮功能可以幫助用戶迅速確定FPGA程序中的瓶頸所在

6、在您的下一次嵌入式原型或設計中使用LabVIEW和NI RIO

NI RIO硬件設備和LabVIEW由于其短周期高可靠的開發(fā)特性,已經在數(shù)以千計的嵌入式原型或工程產品中得到成功應用。當您在計劃下一次的嵌入式設計時,請考慮這樣一套功能強大、擴展性強的成熟系統(tǒng)為您所帶來的時間和金錢成本上的節(jié)省,以及LabVIEW的圖形化編程、內置的定時特性以及數(shù)以百計的IP內核幫助您縮短的開發(fā)周期。

粵公網安備 44030902003195號

粵公網安備 44030902003195號