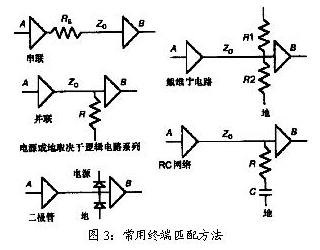

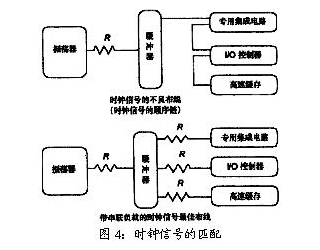

為了抑制出現在印制線終端的反射干擾,除了特殊需要之外,應盡可能縮短印制線的長度和采用慢速電路。必要時可加終端匹配。終端匹配方法比較多,常見終端匹配方法見圖3所示。根據經驗,對一般速度較快的TTL電路,其印制線條長于10cm以上時就應采用終端匹配措施。匹配電阻的阻值應根據集成電路的輸出驅動電流及吸收電流的最大值來決定。時鐘信號較多采用串聯匹配,見圖4所示。

3.7、保護與分流線路:

在時鐘電路中,局部去耦電容對于減少沿著電源干線的噪聲傳播有著非常重要的作用。但是時鐘線同樣需要保護以免受其他電磁干擾源的干擾,否則,受擾時鐘信號將在電路的其他地方引起問題。

設置分流和保護線路是對關鍵信號(比如:對在一個充滿噪聲的環境中的系統時鐘信號)進行隔離和保護的非常有效的方法。PCB內的分流或者保護線路是沿著關鍵信號的線路兩邊布放隔離保護線。保護線路不僅隔離了由其他信號線上產生的耦合磁通,而且也將關鍵信號從與其他信號線的耦合中隔離開來。

分流線路和保護線路之間的不同之處在于分流線路不必兩端端接(與地連接),但是保護線路的兩端都必須連接到地。為了進一步的減少耦合,多層PCB中的保護線路可以每隔一段就加上到地的通路。

3.8、局部電源和IC間的去耦:

在直流電源回路中,負載的變化會引起電源噪聲。例如在數字電路中,當電路從一個狀態轉換為另一種狀態時,就會在電源線上產生一個很大的尖峰電流,形成瞬變的噪聲電壓。局部去耦能夠減少沿著電源干線的噪聲傳播。連接著電源輸入口與PCB之間的大容量旁路電容起著一個低頻干擾濾波器的作用,同時作為一個電能貯存器以滿足突發的功率需求。此外,在每個IC的電源和地之間都應當有去耦電容,這些去耦電容應該盡可能的接近IC引腳,這將有助于濾除IC的開關噪聲。

配置去耦電容可以抑制因負載變化而產生的噪聲,是印刷電路板的可靠性設計的一種常規做法,配置原則如下:

(1)、電源輸入端跨接10~100μF的電解電容器。如有可能,接100μF以上的更好。

(2)、原則上每個集成電路芯片都應布置一個0.01μF的瓷片電容,如遇印制板空隙不夠,可每4~8個芯片布置一個1~10μF的鉭電容。這種器件的高頻阻抗特別小,在500kHz~20MHz范圍內阻抗小于1Ω,而且漏電流很小(0.5μA以下)。最好不用電解電容,電解電容是兩層溥膜卷起來的,這種結構在高頻時表現為電感。

(3)、對于抗噪能力弱、關斷時電源變化大的器件,如RAM、ROM存儲器件,應在芯片的電源線和地線之間直接接入高頻退耦電容。

(4)、電容引線不能太長,尤其是高頻旁路電容不能有引線。

去耦電容值的選取并不嚴格,可按C=1/f計算:即10MHz取0.1μF。對微控制器構成的系統,取0.1~0.01μF之間都可以。好的高頻去耦電容可以去除高到1GHz的高頻成份。陶瓷片電容或多層陶瓷電容的高頻特性較好。

此外,還應注意以下兩點:

(1)、在印制板中有接觸器、繼電器、按鈕等元件時.操作它們時均會產生較大火花放電,必須采用RC吸收電路來吸收放電電流。一般R取1~2kΩ,C取2.2~4.7μF。

(2)、CMOS的輸入阻抗很高,且易受感應,因此在使用時對不用端要通過電阻接地或接正電源。

3.9、布線技術:

3.9.1、過孔

過孔一般被使用在多層印刷電路板中。當是高速信號時,過孔產生1到4nH的電感和0.3到0.5pF的電容。因此,當鋪設高速信號通道時,過孔應該被保持絕對的最少。對于高速的并行線(如地址和數據線),如果層的改變是不可避免,應該確保每根信號線的過孔數一樣。

3.9.2、45度角的路徑

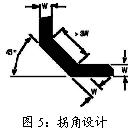

與過孔相似,直角的轉彎路徑應該被避免,因為它在內部的邊緣能產生集中的電場。該場能耦合較強噪聲到相鄰路徑,因此,當轉動路徑時全部的直角路徑應該采用45度。圖5是45度路徑的一般規則。

粵公網安備 44030902003195號

粵公網安備 44030902003195號